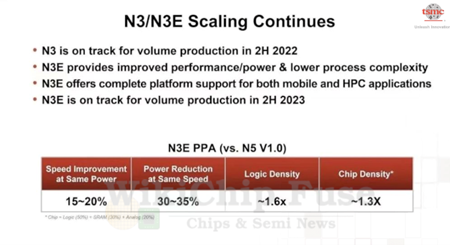

Yes, there will be progress but that’s not really what Moore’s Law is about. Moore’s Law is not an observation that there will be progress eventually but an observation at specific rate of that progress. It’s not “transistors will double eventually”, or “transistors will increase somewhat every 2 years”.

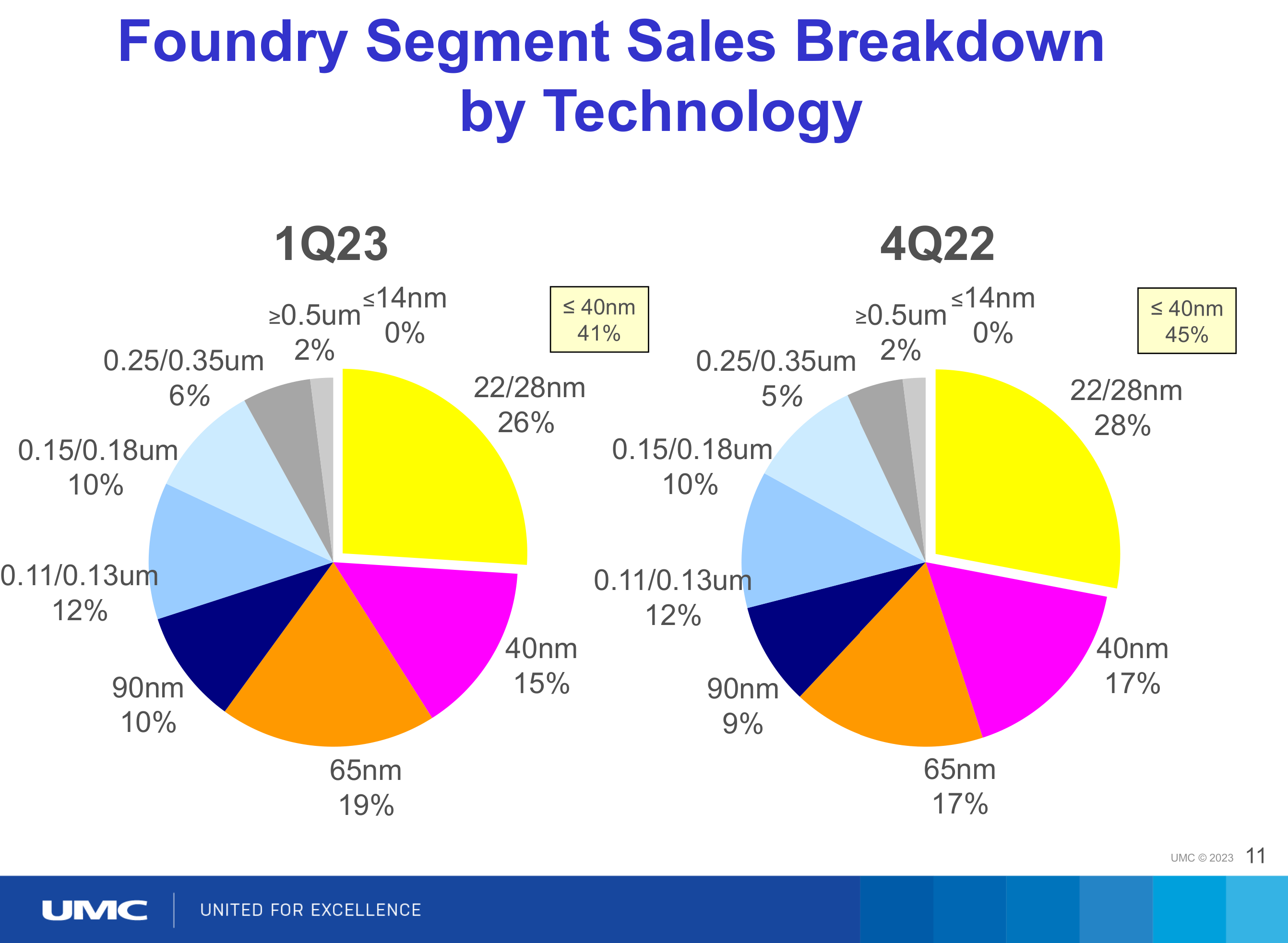

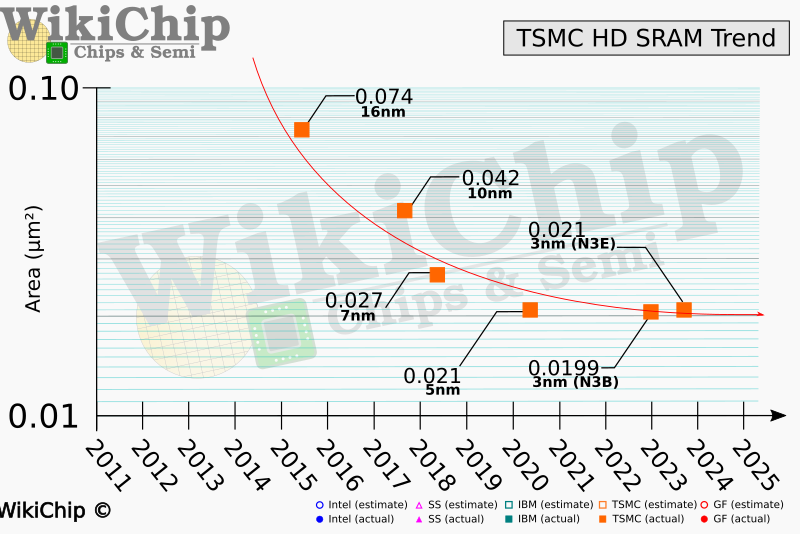

With exponential growth, the tiniest decrease compounds to a major difference. 2 to the power of 3 is 8; the A16 has 16B transistors not 26B. That’s with the gains of the last DUV nodes, 16->10->7nm. EUV to EUV, 5nm to 3nm doesn’t match up to that. It seems transistor growth with EUV nodes is becoming linear so not really in line with the exponential growth of Moore’s Law.

The chips could be larger but flagship phones would have to become even more expensive, and physically larger to dissipate the extra heat. Dennard Scaling mattered more in practice than Moore’s Law ever did but that ended over a decade ago. At the end of the day, all the microarchitecture and foundry advances are there to deliver better performance for every succeeding generation and the rate of that is definitely decelerating.

In 3 years, the only Android chip that has a perceivable difference in performance from the Kirin 9000 is the 8 Gen 2, which cost $160 just for the chip. That performance difference isn’t even enough to be a selling point; the Mate 60 Pro is in the same price range as those 8 Gen 2 phones yet is still perfectly competitive in that market segment.

Neoliberals will do anything to downplay or outright deny any historical incident where import substitution lead to industrialization. Creating captive markets for the dumping of manufactured products was one of the prime drivers of colonialism, which continued under neocolonialism. With sanctions, the US is unintentionally undermining their own hegemony. Businesses like having access to markets and moats. They are giving moats to one side and stripping access to the other.

Sanctions will do for Chinese chip makers what the great firewall did for Chinese internet giants.

Seeing /u/dylan522p acknowledge reality somewhat is refreshing although the conclusion is the predictable “Washington is just sanctioning wrong, if they followed my foolproof sanction regime it would magically work”. Liberals attacking him for this article is quite hilarious. They’re really intolerant of even the slightest deviation from US state department rhetoric.